Faculty of Computer Science, Institute of Computer Engineering, Chair of Adaptive Dynamic Systems

# Low Power Image Processing Applications on FPGAs using **Dynamic Voltage Scaling and Partial Reconfiguration**

Ariel Podlubne, Julian Haase, Lester Kalms, Gökhan Akgün, Muhammad Ali, Habib ul hasan Khan, Ahmed Kamal and Diana Göhringer Technische Universität Dresden, Germany

{ariel.podlubne, julian.haase, lester.kalms, goekhan.akguen, muhammad.ali, habib.khan, ahmed.kamal, diana.goehringer}@tu-dresden.de

#### Abstract

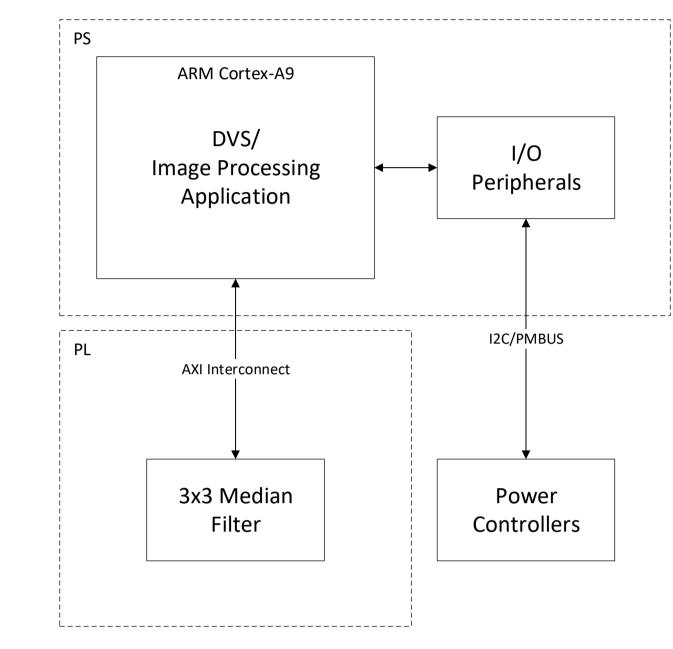

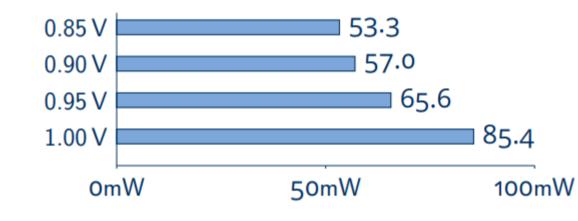

### Dynamic Voltage Scaling

Used for power management at run-time.

The TULIPP project aims to facilitate the development of embedded image processing systems with real-time and low-power constraints. In this work, several adaptive dynamic run-time techniques for reconfigurable SoCs are described. These methods are used for low power image processing applications on high-performance embedded platforms. Dynamic Voltage Scaling (DVS) and Dynamic Partial Reconfiguration (DPR) target the low-power requirements of the embedded systems while debugging supports the fast development on the hardware side of the system. The proposed techniques were tested and verified using an own developed custom SDSoC image processing library.

#### Overview

- Low power image processing applications on the EMC<sup>2</sup>-TULIPP platform.

- Meeting the Real-time requirements through FreeRTOS.

- Implementation of a parameterizable and streaming based High-Level Synthesis image processing library.

- Reduction of power consumption through the run-time techniques **Dynamic Partial Reconfiguration and Dynamic Voltage Scaling.**

- More visibility through self-developed Debugging system.

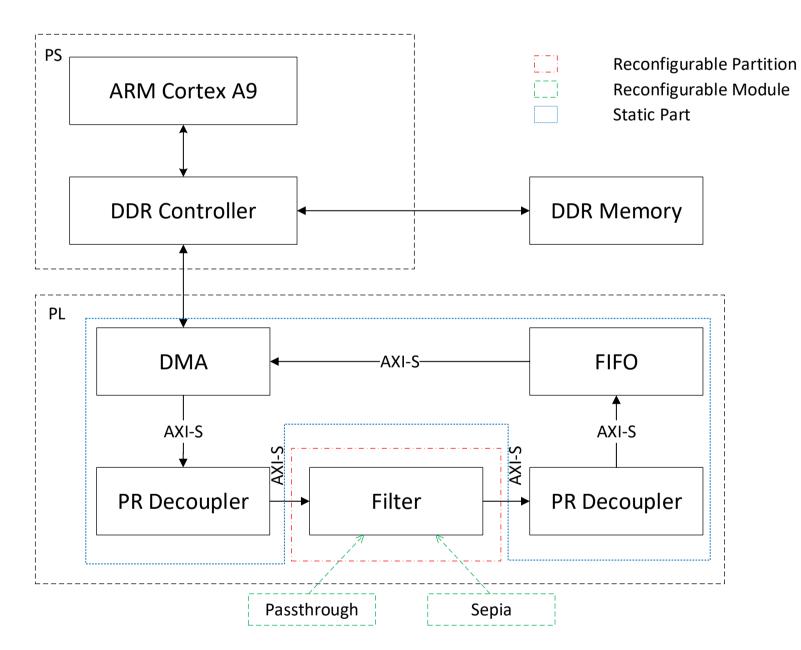

## **Dynamic Partial Reconfiguration**

Power optimization through Dynamic Voltage Scaling (DVS) application running on **Processing System (PS).**

• Power reduction of Programmable Logic (PL) by 37.6%.

| Resource | Used  | Total  | % Utilization |

|----------|-------|--------|---------------|

| BRAM     | 18    | 140    | 12.9          |

| LUT      | 9842  | 53200  | 18.5          |

| FF       | 11984 | 105400 | 11.3          |

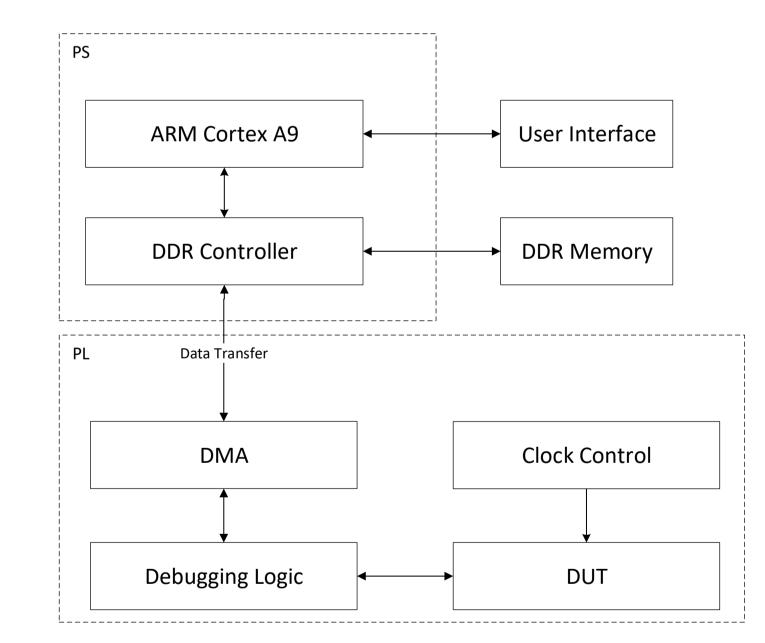

## **Debugging System**

- Used to change the functionality of a selected area

- Control the Dynamic Partial Reconfiguration process from the Processing System (PS).

- Main features of Dynamic Partial Reconfiguration:

- Reduction of power consumption

- Increase hardware resources sharing.

- Change the filter behaviour without halting the complete system.

Value Parameter Partial Bitstream Size 1250 Kbytes **Reconfiguration Time** 10 MS

- Hardware suffers from inherent invisibility.

- Provision of full visibility through effectively unlimited debug window.

- Main features of the debugging system:

- Resource efficient debugging with multiple options of trace window.

- Lossless debugging regardless of the trace window.

| Window | Resource | Used | Total  | % Utilization |

|--------|----------|------|--------|---------------|

| 64     | BRAM     | 9    | 265    | 3.4           |

| 64     | LUT      | 2617 | 78600  | 3.3           |

| 64     | FF       | 3757 | 157200 | 2.4           |

| 1024   | BRAM     | 18   | 265    | 6.8           |

| 1024   | LUT      | 3136 | 78600  | 4             |

| 1024   | FF       | 4134 | 157200 | 2.6           |

### **Further Information**

Ariel Podlubne, Julian Haase, Lester Kalms, Gökhan Akgün, Muhammad Ali, Habib ul hasan Khan, Ahmed Kamal and Diana Göhringer. "Low Power Image Processing Applications on FPGAs using Dynamic Voltage Scaling and Partial Reconfiguration". 2018 Conference on Design and Architectures for Signal and Image Processing (DASIP), Porto, 2018

#### Acknowledgement

The work described in this poster has been supported in part by European Union's Horizon 2020 research and innovation program project Towards Ubiquitous Low-power Image Processing Platforms (TULIPP) under grant agreement number 688403 and in part by the German Federal Ministry of Education and Research BMBF under grant agreement number 16KIS0666 SysKit\_HW.