**REFERENCE:** TULIPP project – Grant

Agreement n° 688403

DATE: 15/05/2018

ISSUE: 2 PAGE: 1/115

# **TULIPP**

H2020-ICT-O4-2015

**Grant Agreement n° 688403**

## D1.2: Reference Platform v2

#### **Authors**

| Organization | Participant          |

|--------------|----------------------|

| THALES       | Philippe Millet      |

| SUNDANCE     | Flemming Christensen |

| IOSB         | Igor Tchouchenkov    |

| HIPPEROS     | Antonio Paolillo     |

| NTNU         | Magnus Jahre         |

| TUD          | Lester Kalms         |

| SYNECTIVE    | Magnus Peterson      |

| Reference: | TULIPP project – Grant |

|------------|------------------------|

| MEFERENCE. | Agreement n° 688403    |

**ISSUE:** 2 PAGE: 2/115

#### Copyright TULIPP CONSORTIUM

## **Reviewers**

| Organization         | Participant       |

|----------------------|-------------------|

| NTNU                 | Magnus Jahre      |

| IOSB                 | Igor Tchouchenkov |

| 1000                 | Boitumelo Ruf     |

| Sundance             | Fatima Kishwar    |

|                      | Graeme Parker     |

| Efficient Innovation | Carlota Pons      |

|                      | Fabien Marty      |

| Description | TULIPP project – Grant |

|-------------|------------------------|

| REFERENCE:  | Agreement n° 688403    |

ISSUE: 2 PAGE: 3/115

Copyright TULIPP CONSORTIUM

# **Document Description**

| Deliverable number        | D1.2                  |

|---------------------------|-----------------------|

| Deliverable title         | Reference Platform v2 |

| Work Package              | WP1                   |

| Deliverable nature        | Report                |

| Dissemination level       | Public                |

| Contractual delivery date | 2017-10-01            |

| Actual delivery           | 2018-05-16            |

| Version                   | 1.2.5                 |

|           | Written by      | Approved by |

|-----------|-----------------|-------------|

|           | Philippe Millet |             |

| Name      |                 |             |

| Signature |                 |             |

|           |                 |             |

|           |                 |             |

| REFERENCE: | TULIPP project – Grant |

|------------|------------------------|

| REFERENCE: | Agreement n° 688403    |

ISSUE: 2 PAGE: 4/115

Copyright TULIPP CONSORTIUM

# **Version history**

| Version | Date       | Description     |

|---------|------------|-----------------|

| 1.0     | 2018-01-31 | Initial version |

| 1.2.5   | 2018.05.16 | Final version   |

|         |            |                 |

|         |            |                 |

## **Executive Summary**

This deliverable presents the current progress towards defining the reference platform. It is the second version of a document that presents the reference platform. In such it extends the first document going towards the final handbook of the starter kit presented in D1.1.

D1.2 must be seen as the first version of the final D1.3 document, therefore from this version to the final one, some parts will be added and some other parts will be improved and extended. More information will be given e.g. more interfaces or more components will be explained and reviewed.

While D1.2 explains the methodology to select and improve the guidelines, D1.3 will reference them.

DATE:

15/05/2018

2

ISSUE:

**PAGE:** 6/115

#### Copyright TULIPP CONSORTIUM

## **Table of Contents**

| 1 | INTR  | ODUCTION                                                 | . 11 |

|---|-------|----------------------------------------------------------|------|

|   | 1.1   | Towards the TULIPP handbook                              | . 12 |

|   | 1.2   | The Functionality                                        | . 13 |

|   | 1.3   | The Trade-offs                                           | . 14 |

|   | 1.4   | The Need for Efficiency                                  | . 16 |

|   | 1.5   | Standardization                                          | . 18 |

|   | 2.1   | Methodology to create guidelines                         | . 23 |

|   | 2.2   | Methodology to select guidelines                         | . 27 |

|   | 2.2.1 | STEP 1: the Guideline Quality Assurance Board            | . 27 |

|   | 2.2.2 | STEP 2: Quality Assurance report                         | . 28 |

|   | 2.2.3 | STEP 3: The Guideline Improvement Expert Board           | . 28 |

|   | 2.2.4 | STEP 4: The guidelines database and guideline references | . 29 |

| 3 | EMB   | EDDED COMPUTING CHALLENGES                               | . 30 |

|   | 3.1   | An Image-processing Platform                             | . 30 |

|   | 3.2   | Medical Challenges                                       | . 32 |

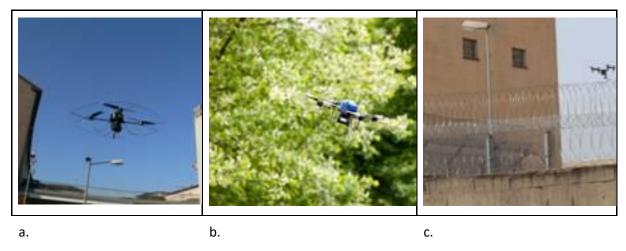

|   | 3.3   | UAV, Drones Challenges                                   | . 33 |

|   | 3.4   | ADAS Challenges                                          | . 35 |

|   | 3.5   | Challenges Conclusion                                    | . 37 |

| 4 | HAR   | DWARE PLATFORMS                                          | . 38 |

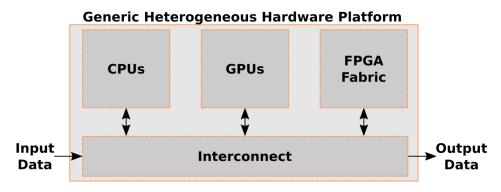

|   | 4.1   | Hardware constraints from the system point of view       | . 38 |

|   | 4.2   | General platform architecture                            | . 38 |

|   | 4.3   | Processors                                               | . 39 |

|   | 4.4   | System on Chip                                           | . 40 |

|   | 4.5   | Processor Modules                                        | . 41 |

|   | 4.5.1 | Physical connectors                                      | . 41 |

|   | 4.5.2 | System on Module (SoM)                                   | . 42 |

|   | 4.5.3 | Embedded System Module (ESM)                             | . 42 |

|   | 4.5.4 | PC/104                                                   | . 43 |

|   | 4.6   | Input / Output Interfaces                                | . 43 |

TULIPP project – Grant Agreement n° 688403

#### Copyright TULIPP CONSORTIUM

|         | 4.6.1 | Camera interfaces                                                                                   | 43 |

|---------|-------|-----------------------------------------------------------------------------------------------------|----|

|         | 4.6.2 | Display interfaces                                                                                  | 43 |

|         | 4.6.3 | Hardware interconnect Protocols                                                                     | 44 |

|         | 4.7   | Scalability of the compute architecture                                                             | 44 |

| 5       | OPEI  | RATING SYSTEM & LIBRARIES                                                                           | 45 |

|         | 5.1   | Low memory footprint                                                                                | 45 |

|         | 5.2   | Scheduling policies                                                                                 | 45 |

|         | 5.3   | Managing hard real-time constraints                                                                 | 46 |

|         | 5.4   | Choosing application programming interfaces                                                         | 46 |

| 6<br>RI |       | JCTURED PERFORMANCE ANALYSIS: MEETING EMBEDDED IMAGE PROCESSING APPLIC MENTS WITH HIGH PRODUCTIVITY |    |

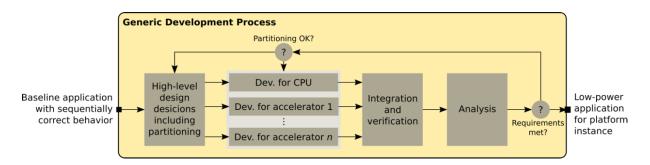

|         | 6.1   | The generic development process                                                                     | 48 |

|         | 6.2   | Selecting performance analysis tools                                                                | 50 |

|         | 6.3   | Programming model selection                                                                         | 50 |

|         | 6.4   | Evaluating performance analysis tools                                                               | 52 |

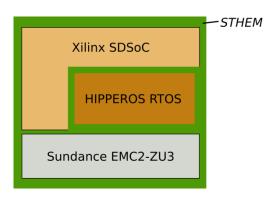

|         | 6.5   | STHEM: The TULIPP performance analysis tools                                                        | 53 |

|         | 6.6   | Tool-chain Standards                                                                                | 56 |

| 7       | PLAT  | FORM, STANDARDS and STANDARDISATION                                                                 | 57 |

|         | 7.1   | The hardware platform choice                                                                        | 57 |

|         | 7.2   | The operating system implementation choices                                                         | 57 |

|         | 7.3   | The toolchain choices                                                                               | 58 |

| 8       | CON   | CLUSION                                                                                             | 59 |

| 9       | APP   | ENDIX: THE GUIDELINES DATABASE                                                                      | 60 |

|         | 9.1   | Adjust the Algorithm to the Underlying Architecture                                                 | 60 |

|         | 9.2   | Choosing a Real-time Operating System                                                               | 62 |

|         | 9.3   | Do Not Turn the FPGA Device On and Off too Frequently                                               | 64 |

|         | 9.4   | Move Data Processing as Close to the Sensor as Possible                                             | 65 |

|         | 9.5   | Should I Use a FPGA or an ASIC?                                                                     | 67 |

|         | 9.6   | Reordering Loops can Reduce Bandwidth Requirements                                                  | 69 |

|         | 9.7   | Upgrading to newer parts/FPGA architectures                                                         | 70 |

|         | 9.8   | Optimize nested loops with early exit by measuring the number of unconditional iterations           | 72 |

2

#### Copyright TULIPP CONSORTIUM

|    | 9.9            | Source Code Organization                                                                                               | 74    |

|----|----------------|------------------------------------------------------------------------------------------------------------------------|-------|

|    | 9.10           | Automating the Toolchain                                                                                               | 75    |

|    | 9.11           | Timestamp ADC samples promptly                                                                                         | 76    |

|    | 9.12           | Save implementation time by delegating customizations to the hardware vendor                                           | 77    |

|    | 9.13           | Selecting PSU to supply the chosen hardware                                                                            | 79    |

|    | 9.14           | Manage to accelerate streaming capable functions in a single accelerators                                              | 80    |

|    | 9.15           | Integrating your image processing HDL code with the platform                                                           | 82    |

|    | 9.16           | Use hil testing rather than wait for a final hardware                                                                  | 83    |

|    | 9.17           | How to get EMC2 Board communicate with an UAV                                                                          | 84    |

|    | 9.18<br>positi | Use an external constant voltage reference for the ADC instead of the internal reference base ive supply voltage (VDD) |       |

|    | 9.19           | Isolate designs to low-power domains to reduce power consumption                                                       | 88    |

|    | 9.20           | Beware the parameters of external data/clocking when testing or debugging                                              | 89    |

|    | 9.21           | Make sure to access streamed data from within accelerated function                                                     | 90    |

|    | 9.22           | Writing for HW                                                                                                         | 92    |

|    | 9.23           | Remove recursion when aiming to parallelize code                                                                       | 94    |

|    | 9.24           | How to optimize sgm for GPGPU                                                                                          | 96    |

|    | 9.25           | Save Intermediate Storage with Dataflow Regions                                                                        | 97    |

|    | 9.26           | When to use conditional branching                                                                                      | 99    |

|    | 9.27           | Do not use floating point computation on FPGA                                                                          | 100   |

|    | 9.28           | Avoid LibTIFF library and use raw image format                                                                         | 102   |

|    | 9.29           | Use EMVA1288 to compare cameras                                                                                        | 103   |

|    | 9.30           | Low latency image processing over TCP IP data stream                                                                   | 104   |

|    | 9.31           | Major challengers to integrating hard real time image processing using neural networks in MI 105                       | PSoCs |

|    | 9.32           | Ensure Dataflow by using Inline Sub-functions                                                                          | 106   |

|    | 9.33           | Data logging using SD Card                                                                                             | 108   |

| 10 | ١              | REFERENCES                                                                                                             | 111   |

| 11 |                | Appendix: Guideline Evaluation Experts                                                                                 | 114   |

TULIPP project – Grant Agreement n° 688403

DATE:

15/05/2018

**ISSUE:** 2 PAGE: 9/115

#### Copyright TULIPP CONSORTIUM

# **List of Figures**

| Figure 1: Example of a guideline                                                                           | 21      |

|------------------------------------------------------------------------------------------------------------|---------|

| Figure 2: Instantiating platforms based on guidelines. The two instances are partially compliant with di   | fferent |

| subsets of guidelines.                                                                                     | 22      |

| Figure 3: The workflow to generate and evaluate guidelines that define the platform instance. The critical | path is |

| shown in red                                                                                               | 23      |

| Figure 4: Guidelines quality improvement process                                                           | 29      |

| Figure 5: The typical usage for an embedded image processing platform                                      | 31      |

| Figure 6: Different obstacles in typical environments of UAVs                                              | 34      |

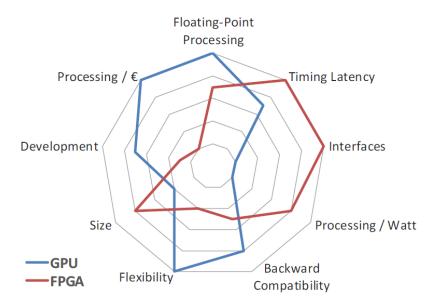

| Figure 7: Qualitative comparison of GPU and FPGA                                                           | 40      |

| Figure 8: Generic Heterogeneous Hardware Platform                                                          | 47      |

| Figure 9: Generic Development process                                                                      | 48      |

| Figure 10: Advantages and Challenges of the SPM and MPM strategies                                         | 51      |

| Figure 11: The Supporting utilities for Heterogeneous Embedded image processing platforms (STHEM)          | 54      |

**REFERENCE:**TULIPP project – Grant

Agreement n° 688403

DATE: 15/05/2018

ISSUE: 2 PAGE: 10/115

#### Copyright TULIPP CONSORTIUM

## **List of Tables**

| Table 1: Energy-efficient Embedded image processing applications challenges                              | . 37 |

|----------------------------------------------------------------------------------------------------------|------|

| Table 2: Limitations of the main TULIPP-PI1 components and needed utilities to alleviate the limitations | . 55 |

| Table 3: Tulipp Expertise Panel                                                                          | 115  |

TULIPP project - Grant Agreement n° 688403 15/05/2018

**PAGE: 11/115** 2

Copyright TULIPP CONSORTIUM

#### INTRODUCTION

Image processing deals with image manipulation, transformation and analysis. This domain takes twodimensional data as an input, whose width, height and pixel depth depend on the sensor. The wide variety of sensors and application types make image processing a complex and deep domain.

The image processing field has already several groups that have been formed with time, all over the world, to deal with sub-domains but no particular focus has been done on low-power. Even though the topic is somehow addressed, it has so far not been the main concern.

While writing about low-power, it must be explained what is meant in this document because any platform might be seen as a low-power platform depending on the domain addressed.

We can also notice that we easily find high-performance targets dedicated to data centres and clouds at the cost of hundreds of watts. At the other end, in the Internet of Things (IoT) realm we can find low-power targets, for less than a watt, but they drastically lack for performance. Yet this is where the "big players" (like Google, Facebook, Amazon, Intel) are today: either high performance computing with higher energy-consumption or ultralow-energy consumption but at the cost of computing performances.

There is nearly a desert in the middle, when one needs a good trade-off between decent-performances and low-enough-power i.e. between 1 watt and 15 watts. We expect this area to develop with the ever growing needs for ADAS systems, but industries with lower volumes (a few thousand pieces a year) might not be able to access the technology. For instance, the Xavier SoC from NVidia is so dedicated to the automotive market and there are so many expectations from the chip manufacturer on this market that it focuses on major customers and sells the SoC only with a strong support for several million euros. The same happens with processors dedicated to smart phones as this market is captive, chips are only sold by millions quantities.

For smaller series of products one needs to find chips that match the processing needs, the price and the power-consumption. When the target has been chosen, image processing engineers still require a good knowledge of what can be done to achieve the best possible trade-off for their algorithm implementation.

The chapter is introducing the goals of the deliverable and explains how to develop an embedded system for image exploitation in real-time as follows: The first step is to get an algorithm that provide a functionality that has to be implemented in a product, the second step is to find trade-offs between the functionality and the physical constraints of the product. When choices have been made, there is

####

ISSUE: 2 PAGE: 12/115

#### **Copyright TULIPP CONSORTIUM**

no choice anymore to redesign the platform. This is the kingdom of optimization for everything must fit and run on the platform at the end.

The main objective of the Tulipp project is to identify the best possible choices for embedded image processing platforms and initiate a path towards standardisation. To this end, the work shown in this deliverable is the bases of a book that will help to promote the ideas of the Tulipp project outside the consortium and leave a legacy after the end of the project. It will strongly express that to build solutions for the embedded image processing domain, one needs to fully understand the constraints of low- and medium-volumes (up to thousands of pieces per year) because it strongly limits the freedom of designers.

#### 1.1 Towards the TULIPP handbook

This deliverable is the first step towards a book that will help engineers to implement such image processing systems fast, efficient and saving development costs.

The book will be what is presented in this deliverable: a collection of knowledge from experts of several fields covering the implementation of product using image processing.

The information addresses both experts and beginners. While a beginner will find most of the book useful, an expert should look at the parts that address topics where he is not an expert. E.g. an expert in image processing algorithms will have interest in reading the part on hardware choice and operating system implementation to understand what trade-off he can make on the algorithm to make it easier to implement, while an expert in operating system will most probably like to read the specificities of image processing algorithms to understand what services should be developed in the operating system.

This future book is also aimed at student to learn from the field of embedded image processing which means computing performance with a limited power budget, or better said power-efficient high-performance image processing.

This deliverable is the first extract of the knowledge shared and owned within the TULIPP consortium. We have got agreements and commitment from other projects to cover several chapters of the book to help us extend the number of topics addressed in the book.

The deliverables D1.2 and D1.3 are two versions of the same document. While D1.2 is a draft document collecting a part of the knowledge, D1.3 will be an almost finished version of the contribution of the TULIPP consortium to the final book.

TULIPP project – Grant

Agreement n° 688403

15/05/2018

2

**PAGE: 13/115**

**Copyright TULIPP CONSORTIUM**

#### 1.2 The Functionality

When starting to develop an application for real-time image processing, one often wonders where to start with. Such an application has indeed complex and contradicting constraints leading to deal with challenging compromises.

Having in mind the services that one wants to deliver, it often starts with a proof of concept application developed on a standard Desktop-PC. The main reason being that then one can concentrate on the algorithmic parts of the application, taking no care of any other constraints like memory size, power consumption and even interfaces for input/output signals. At this step the only concern is to have MatLab or C code giving the expected functional results. This proof of concept shall not even run at real-time, which means it shall not process the input at the speed of a real-life sensor and can afford to be much slower. The input data is often taken from a file and can be generated with environmental simulators or recorded from a real sensor.

This first instance of the code is developed and linked against standard libraries so that the abstraction level is high enough to play with the parameters of the algorithms only, taking no care of any optimization.

This first step must really be seen as a step leading to the specifications of the functionalities. A danger would be to consider this first step as a first implementation of the algorithm on a target. Even though the code resulting from this step runs on a computer, it is far from being the finale platform of the product. The constraints are clearly different and the resulting software will also have to be very different. Developers and managers must clearly understand that the code resulting from this step will have to be rewritten to fit and run on an embedded system.

Some developers are very keen on using various high-level libraries and development techniques known only to experts, requiring many years of training. On one hand, this allows them to be very efficient and faster produce solutions that they can exploit to develop new functionalities and validate their ideas. Those libraries are often quite complex with many functions, many data structures representing hundreds of thousands of lines of codes spread over hundreds of files. Even with open source libraries one has to face the difficulty to reverse engineer them. A wrong idea would be to think that these libraries should be ported to the embedded system to ease the porting of the application.

At this step, the right word would be "to implement" the application on the target rather than "port" the application. Practically, the application must be redesigned to rely on the embedded libraries and operating system. The way to "translate" the application from the functional code to the embedded code depends strongly on the target itself. The software stack implemented on the target requires making choices almost as impactful as choices for the hardware architecture.

A practical approach is to keep the two spaces separate: One time for functionality, one time for implementation on the embedded product.

When the functionalities are satisfying the functional requirements, the main information for the next step is to be able to extract from the specifications of the algorithm the required computing performances (e.g. number of operation per seconds, input and output throughput...), reference stimulation data (sample input data) and reference output data (the results given by the algorithm from the reference stimulation data).

#### 1.3 The Trade-offs

With a clear view of the required computing performances and the product constraints, one can start designing the platform.

The first step here is to get an understanding of all the constraints of the product. Some constraints, like power-consumption, are more obvious for engineers – because it directly impacts the design of the system – than some others, like the price – because it indirectly impacts the design and, for some expensive products, less impactful. Therefore, understanding all the consequences of a choice is crucial. Let's take the example of a chip, which is one of the most important parts of hardware design.

As hardware design teams are dealing with embedded products, they are often limited by the batteries life time and so by the power consumption, but even when the product has access to the electrical grid it is limited by the thermal dissipation of the heat sink, the cabinet and the packaging. Both the power consumption and the thermal dissipation will limit the type of chip that can fit the system. A short way to express this goal could be: the "lighter" the chip, the better.

At the other end, the software design teams have more and more functionalities with more complexity and have to deal with bigger and bigger data sets. There is no other choice for them; everything has to be implemented on the hardware platform. A hardware that would be unable to run the application and provide the functionalities would be of no help and would have to be redesigned. Thus, for software teams, more computing resources means less difficulties to implement the functions, more available memory means easier access to the data and easier scheduling. A short way to express this goal could be: the "heavier" the chip, the better.

Project and product line managers have to deal with customers. They want the product to fit the costs and they need it to be delivered on time. Any delay will cost money and give more time to competitors to develop the same functionalities on their products. Managers have to take costs into accounts. Costs are divided into two categories: the Non-Recurrent Costs (NRC) and the Recurrent Costs (RC).

TULIPP project – Grant

REFERENCE: Agreement n° 688403

DATE: 15/05/2018

ISSUE: 2 PAGE: 15/115

#### **Copyright TULIPP CONSORTIUM**

NRCs are costs involved during the development phase of the product. Thus if one needs more time than ones competitors to develop the same functionalities, the NRC will be higher than the one of the competitors. Higher NRCs might not be a problem when one develops big series of products, but when one develops only few pieces a year, one has to take great care of the NRCs and reduce them as much as possible while it will have a greater impact on the final product price since it has to be divided by the number of pieces that will be produced. A short way to express this goal could be: the easier to program the chip, the better.

RCs are costs involved during the production phase of the product. Thus it strongly depends on the choices made at design time. More expensive components mean higher prices. Higher RCs will always impact the final product price but unlike the NRC one has to take greater care with larger-series and is even critical for mass production where each cent saved on a product will lead to millions in gained in revenue for the company. A short way to express this goal could be: the "cheaper" the chip, the better.

While some of the constraints will lead the hardware designers to prefer domain specific chips delivering more computing per watt with higher power-efficiency; other constraints would lead them to choose more general purpose processors because they are easier to program and will help to deliver faster the product. Some dedicated chips like Field Programmable Gate Arrays (FPGAs) will often offer higher efficiency at the cost of longer developments and higher component prices. The matter is further complicated by system software: A more complex chip with a better operating system and more convenient development tools may result in lower development time than a simpler chip with less mature system software. So the designer must find the trade-offs that allows for implementation of the algorithm with corresponding performance at a given price with the thermal or energy budget that is allowed in the system.

A trade-off does not mean the hardware designer has to find a solution that matches all the constraints. More than often he has to discuss the constraints and move the thresholds. If the functionalities cannot all be implemented; check if it is possible to remove some of them or reduce the effectiveness or the accuracy of the functions within certain margins. Reducing the accuracy from 1% or 2% might in some case reduce the load from several tens of percentage points and allow for using smaller and cheaper chips.

For real-time image processing, the main problem is data throughput and memory size. Images are 2D-data. For colour images, a pixel is often described with a 32-bit word. The total quantity of data to move between memory layers for each function might be tremendous. The processing element is not the only one element to be taken into account while designing the system. The whole hardware architecture must be studied carefully. The memory size, the bus width and the type of IOs are as important as the processing element. Each hardware element will most likely also give constraints on other hardware elements and impact the final architecture choices.

#### 1.4 The Need for Efficiency

The first step to select the hardware platform is to know the targeted price. This selection will be done taking into account the number of products per year. Another primordial factor is the energy budget, the battery life-time and/or the thermal dissipation. With those two figures, price and energy-budget, a first selection of targets can be done. The energy budget is often linked with weight while higher power consumption means more energy storage resulting in heavier batteries. Heavier batteries will also be bigger and take more volume. Bigger volume and weight will require a redesign of the system. If the computer is embedded on a flying drone, the additional volume deteriorates flight characteristics and weight reduces fly time very strong.

The second step is to deal with the needed computation resources. This is not as easy as it seems. Many years ago, we used to look at the clock frequency to compare General Purpose Processor (GPP) performance while we were looking at the number of Multiply-Accumulate (MAC) per seconds for Digital Signal Processors (DSP). DSPs were compared with FPGAs also using MAC/s values while FPGAs were compared one to another according to the number of Look-Up Tables (LUTs), logical cells and DSP blocks (a DSP block is an element inside the FPGA that offers multiply and accumulate capabilities and should not be confused with the DSP processor which is a chip).

With the emergence of multi-core and many-core architectures, the concurrency to access IOs and memory limits the cores and their computing performance as they have to enter idle states to wait for data. The characteristics of the chip have to be tested according to each user application profile for they may use the resources in very different ways. In order to get representative figures and measurements, one must test the chip with benchmarks representative of the final applications. The characterisation of the memory bandwidth and the measurement of the performance of the cores for several basic functions with several data set sizes are a good way to proceed. For instance, one may test Fast Fourier Transforms (FFTs) with several sizes and check how the core performance will be affected by the size of the data set while with this kind of function the distance between data increases with the size of the data set.

Some processors also have accelerators for dedicated basic functions. An example of such an accelerator is the Streaming SIMD Extension 2 (SSE2) implemented on the Intel processors. An SIMD is a set of cores processing a Single Instruction on Multiple Data. It means there is one controller that sends the same instruction to many processing cores. Each core, at each cycle will execute that instruction with data that are different from the one received by other cores. This kind of processor is very energy-efficient as the control is reduced to its minimum, but the efficiency requires that the application can be data-parallelized. There is usually a reduced set of instructions that can be handled by the processing cores. This kind of accelerator must be used when available because they allow using

REFERENCE: TULIPP project – Grant

Agreement n° 688403

DATE: 15/05/2018

**ISSUE:** 2 PAGE: 17/115

#### **Copyright TULIPP CONSORTIUM**

all the available computing resources which gives the best possible performances. When one would only use the general purpose processor he would consider the chip not suitable for the application while it could actually be if the test were fairly done. Most of the time, the difficulty for using such accelerators comes from the tools. The hardware often offers new functionalities long before they have time to be integrated in the tools. When the SSE2 was just implemented on Intel processors, one had to write assembly code to access the hardware accelerator while today it is taken in charge in compilers. The same happens today with the Myriad processors which efficiency and best performances is only available to well-trained programmers.

Another possibility to access the best performance is to use vendor libraries. General Purpose Graphic Processor Units (GP-GPU) are able to compute almost any kind of function and are extremely parallel. They are designed to efficiently schedule the memory access so that the cores are waiting as little as possible. Doing so, they maximize the utilisation of their cores. One way to implement an FFT on these processors is to program it manually with a dedicated language (CUDA or OpenCL). But the best efficiency is usually achieved with the library delivered together with the component.

Memory size and memory hierarchy is also an important factor to take into account while designing a hardware platform. Since one of the main problem for parallelism is data access, the closer the memory to the core the better. But having memory close to a core does not solve the global problem of data access and data movement. Because the memory size given to a core will never be enough to store the complete set of data given to a function for a given application, it is necessary either to have "big" memory spaces or to be able to process the data as they are streamed out of the sensors.

"Bigger" memory means more possibilities to store the data but at the same time higher latency to access them and also more power consumption. Streaming at the other end will allow for shorter latency and lower power consumption, but might not allow some algorithm to be implemented, e.g. if one needs to compute an average on the complete image to shift the histogram i.e. add or subtract this value to every single pixel of the image. Then, one needs to be able to store the whole image and have no choice but to implement a memory big enough for that purpose.

Depending on the criticality of an application, the underlying platform will be totally different. When, for instance, one needs to be able to master hard real-time deadlines, meaning missing a deadline is not allowed, one will not enable the cache in the processors. Although the processor cache is meant to better feed the processor with data and by this means increases the performance of the hardware, it is also, at the same time, not possible to characterize properly and will result in impossibilities to know the behaviour of the application at design time. This goes also with the number of cores that are used on a symmetrical multi-core chip. The need of knowing the behaviour at design-time and ensuring that this behaviour is the same at run-time, requires composability in the platform. This is not

# REFERENCE: TULIPP project – Grant Agreement n° 688403 DATE: 15/05/2018

ISSUE: 2 PAGE: 18/115

#### **Copyright TULIPP CONSORTIUM**

compatible with current implementations of multi-core processors because cores will have concurrent access to the memory and make the global application behaviour unpredictable.

On the other hand, both the cache mechanism and the multi-core architecture allow higher average performance and will be helpful when only the performance matters. They will also allow for higher energy-efficiency in terms of performance per watt.

So the efficiency one can get from the platform depends highly from the requirements of the application.

#### 1.5 Standardization

Standards are the key to easier platform integration and wider acceptance and utilisation of a solution. There are a lot of examples of widely used interfaces (USB, Ethernet, ...), used every day and allowing us to share data and work. However, we might wonder how these standards became so popular.

To spread widely, a standard must fill a need and/or be easy to use. However, it may still fail because of royalty fees. A good example is HDMI. The format is good and quite widely accepted but with one needs to pay to implement an HDMI interface. This is how DisplayPort came up. As it is royalty free, anyone can implement this interface without having to pay. And because of the fees, two standards are now fighting one another making life difficult during meetings when a computer has to be plugged to a screen and converters are needed to interface them. Open standards is a good way to avoid this and it helps to promote and improve a standard because anyone can access it and join the effort of defining. The drawback is to deal with other companies with other constraints to define the standard but the benefits of compatibility and lower prices overrides the decision.

Some companies are voluntarily not using standards in order to prevent anyone to connect anything on the platform. This is for instance the strategy of Apple that wants to keep control of the platform and do not allow for anyone to connect anything to their computers. Thus they design interfaces and plugs that are only compatible with other Apple equipment. However, even Apple uses WLAN, Bluetooth and USB standards as they need to communicate with devices from other companies.

Before starting to envisage the concept of a new standard, one must have a deep look at existing solutions. There might already exist standards that are almost satisfying the needs. If they would not fit completely, they might be adapted to fit better new environments.

For instance, let's have a look at the PCle standard. There have been several improvements from the first version in 2003 (v1.0) to the very last proposed specifications in 2017 (v5.0) of this standard to cope with new needs, new performances and new applications and to use new capacities allowed by

REFERENCE: TULIPP project – Grant Agreement n° 688403

DATE: 15/05/2018

**ISSUE:** 2 PAGE: 19/115

#### **Copyright TULIPP CONSORTIUM**

technology improvements. From v1.0 to v5.0, the throughput has been multiplied by about 15 while improvement was also done to reduce the power consumption during idle periods but not yet to cope with low-power applications. One expected, still in draft extension of the standard is the Mobile PCle specification (M-PCle) where power consumption would roughly scale with the amount of data transferred. Rather than creating an ad hoc interconnect that would fit low-energy consumption for embedded devices, one has first to check if existing standards are evolving towards this goal and evaluate if they would match the requirements. This is what the TULIPP project evaluates through this document.

#### 2 THE GUIDELINES:

#### A path towards standardisation in the low-power image processing system domain

The initial approach was to use the interfaces of the TULIPP platform instance to create a basis for later standardisation efforts. Although this approach is valid and an interesting starting point (see Section 7), we are concerned that it will not result in a universally applicable standard for low- and medium-volume image processing systems. The reason is the heavily constrained design environment of these systems. Image processing applications need to achieve high performance while meeting strict cost, energy, power and physical size constraints (see Section 1.3 for a detailed discussion). A standard that does not have sufficient flexibility to meet these constraints for a wide range of applications is doomed to fail. To reduce the impact of this problem, we came up with the idea of guidelines.

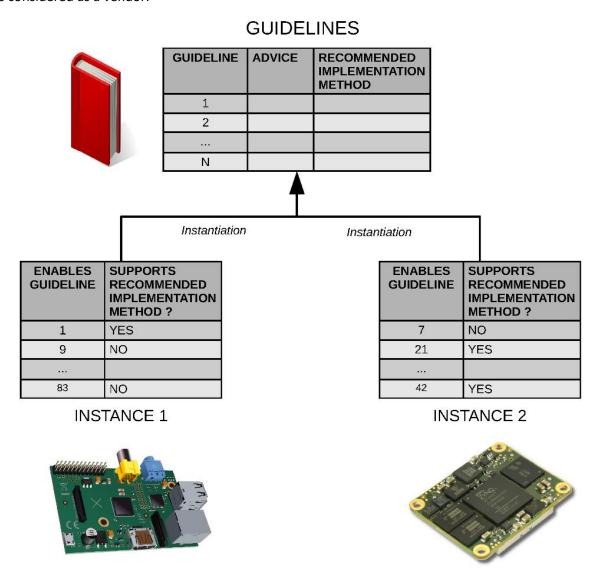

A guideline is an encapsulation of an *advice* and a *recommended implementation method*. The advice captures expert insights in a precise, context-based formulation and orients the follower (the person reading the advice) towards a goal. The recommended implementation method suggests interfaces and steps that work well in practice to implement the advice. The guidelines will help a standardisation body, such as the EMVA, transform the interface-driven description provided by the reference platform into a viable standard. The guidelines provide a basis the standardisation body can use to engage in informed discussion with key stakeholders across the European low- and medium-volume image processing industry. This initiative has already started during the TULIPP project with the setup of an ecosystem of 20+ stakeholders across Europe; most of them are already members of various associations like EMVA. Thus, the guidelines provide a necessary context for adapting the interface-specification of the reference platform into a highly successful European standard.

Both the advice and the recommended implementation methods are supported by theoretical and experimental evidence that is either gathered within the project or is pre-existing in the community. The advice in a guideline is essentially inarguable since it is based on proofs and facts. However, it is not necessary to treat the recommended implementation method as a strict rule. Using alternative implementation methods or new tools is allowed and encouraged.

- · **Advice**: Exploit both vectorization and multithreading for high performance on multicore processors with vector units such as the ARM Cortex A9. On these architectures, utilizing all hardware execution resources is key to achieve high performance [2] [4, 5].

- Recommended implementation method: Use OpenMP. OpenMP is a widely supported parallel programming API that enables programmers to express vectorization and multithreading operations concisely using compiler directives. Programmers need not worry about specifying scheduling and synchronization operations in code. These are handled transparently by the OpenMP runtime system. See the official OpenMP examples[6] to understand in more detail about exploiting vectorization and multithreading simultaneously.

Figure 1: Example of a guideline

Figure 1 contains an example of a guideline for obtaining high performance on multicore processors with vector units.

In the guideline example in Figure 1, the advice orientates the follower towards the goal of achieving high performance in the specific context of multicore processors with vector units. The advice advocates simultaneously exploiting all execution resources for higher performance and provides experimental evidence as support. The recommended implementation method points to OpenMP as a productive choice and links to usage examples.

Guidelines stem from expert insights in image processing and embedded system domains and cover performance, power, and productivity aspects. Generation and evaluation of guidelines is discussed in detail in Sections 2.1 and 2.2.

Guidelines may overlap or exclude one another as a natural consequence of the vast design and implementation spaces for low power image processing. Overlapping guidelines are those whose advice are based on the same underlying principle, or those whose recommended implementation methods are the same. Exclusion occurs when a pair of guidelines point in different but equally competent directions to reach the same goal.

Guidelines are targeted towards both developers and vendors. Developers conform to the guidelines by paying attention to the encapsulated advice and considering recommended implementation methods. Vendors ensure recommended methods are available in their products to attract developers. If implementing recommended methods is infeasible due to constraints, then developers and vendors can consider alternative methods.

We call the process in which a vendor identifies or implements recommended methods compliant with a relevant subset of guidelines as *instantiation*, as shown in Figure 2. The output of instantiation

process is an *instance*. The platform instance is an example of instantiation if the project consortium is considered as a vendor.

Figure 2: Instantiating platforms based on guidelines. The two instances are partially compliant with different subsets of guidelines.

An instance can be *partially compliant* or *fully compliant* with the guidelines. A partially compliant instance provides alternative methods to implement guidelines, whereas a fully compliant instance provides only recommended implementation methods for the guidelines it supports. Both instances in Figure 2 are partially compliant. The platform instance is an example of a fully compliant instance since it provides only recommended implementation methods for the guidelines it supports.

**Copyright TULIPP CONSORTIUM**

It is important for vendors to note that an effort to support the complete set of guidelines is not recommended. Support for all guidelines will likely lead to an over-designed instance that is no longer relevant to the application and violates hard constraints such as cost and total power consumption.

#### 2.1 Methodology to create guidelines

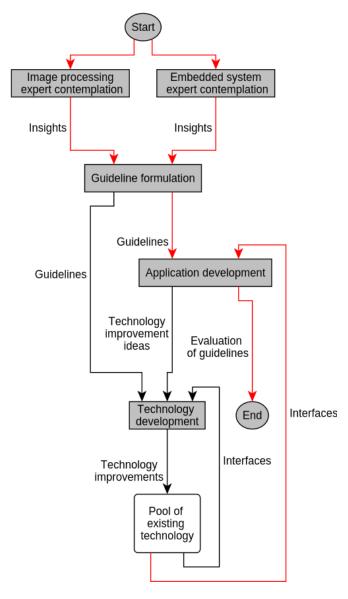

Figure 3: The workflow to generate and evaluate guidelines that define the platform instance. The critical path is shown in red.

Figure 3 shows our guideline production workflow. The requirements of the workflow are that it should (a) generate guidelines for low power image processing, (b) evaluate the guidelines, and (c) be aligned with all project objectives. As evident from the illustration, the workflow captures project-wide effort towards a common vision.

We explain the different steps involved in the workflow starting with the critical path next.

1. Image processing and embedded system domain expertise: The workflow starts by gathering insights from experts in the domains of image processing and embedded systems. Insights refer to deep, underpinning knowledge that come from experience and modelling. The expertise required to produce insights is not restricted to the project partners. External experts such as those in the advisory board can also contribute with insights. Insights have no restrictions on format and can be expressed in any enlightening manner. The key areas of interest are low power, high performance, and high productivity.

**Insight**: Real-time OS (RTOS) provide determinism often at the cost of performance.

As a running example of the workflow, consider the insight expressed by an embedded systems expert as a single line of text:

2. Guideline formulation: Gathered insights are analysed and formulated into guidelines. This involves judging the context and orientation of insights, translating them into advice, and deciding on a recommended implementation method. Translation is necessary since guidelines are goal-oriented, precise, and context-based whereas insights have no restrictions on their format. There is no one-to-one mapping between a guideline and an insight. Many insights can coalesce to produce a guideline, or a single insight can be fertile enough to produce several guidelines.

| REFERENCE: | Agreement n° 688403 |

|------------|---------------------|

|            | 0                   |

**ISSUE:** 2 PAGE: 25/115

#### Copyright TULIPP CONSORTIUM

- **Advice**: Balance between deterministic execution and performance while setting realtime OS (RTOS) parameters[1].

- **Recommended implementation method**: Configure the RTOS using vendor suggested methods[3]. Test and document candidate configurations extensively.

Continuing the running example, the insight is translated into the following guideline:

3. Application development: In this step, guidelines formulated are implemented within the applications and evaluated for impact. In the context of the project, the applications are the project applications part of the starter kit. Guidelines are implemented either using recommended or alternative methods. We assume that interfaces from existing technology are adequate to implement guidelines, but also recognize that existing interfaces might lack productivity. In the context of the project, technology to implement guidelines is made available through the platform instance. Guidelines are evaluated for goal orientation, the suitability of the recommended implementation method, and arguments for choosing alternative methods. We expect that all formulated guidelines will be evaluated in one or more applications since they have a common driving theme – low power high performance real-time image processing. Once all guidelines are evaluated, the workflow ends.

An excerpt from a possible evaluation of the guideline formulated in the running example could read as follows:

The medical image processing application missed 20/100 deadlines when the default Linux kernel 4.7.2 provided by Xilinx was used. No deadlines were missed under the HIPPEROS RTOS configured with the Least Laxity First scheduling policy, but performance was restricted to 8 FPS, well under the required 24 FPS goal. Enabling multicore execution (SMP) and a hybrid scheduling policy with both data locality and laxity awareness increased performance to 28 FPS with no deadlines missed – a clear win for HIPPEROS. We configured HIPPEROS using the HIPPEROS configuration plugin provided by the project for Xilinx SDSoC 2016.2.

4. Technology development: This is the only step of the workflow that is not on the critical path. In this step, existing technology is improved to enable productive implementation of

| Decemen    | TULIPP project – Grant |

|------------|------------------------|

| REFERENCE: | Agreement n° 688403    |

**ISSUE:** 2 PAGE: 26/115

#### **Copyright TULIPP CONSORTIUM**

guidelines during the application development step. The stimulus to improve existing technology comes from application developers in the form of technology improvement ideas. The improvements aim to increase the productivity of recommended implementation methods to levels that can compete with alternative methods. When recommended implementation methods promise high productivity, developers need not waste time deciding on more productive alternatives. Vendors are more likely to provide recommended implementation methods in their platforms to gain higher compliance. In the context of the project, technology improvements are delivered through the platform instance.

Examples of potential technology improvements include application specific evaluation boards, high performance library routines and custom IP blocks for image processing, low power enabling patches to RTOS schedulers, improved performance analysis techniques for Zynq SoC, workflow tweaks for Xilinx SDSoC etc.

The HIPPEROS configuration plugin provided by the project for Xilinx SDSoC 2016.2 is the technology improvement demonstrated in the running example in the previous step.

The workflow is not iterative since there are no feedback paths or cycles. Feedback is unnecessary since guidelines are based on proofs, facts and expertise. In addition to being feed-forward, the workflow proceeds in a pipelined manner. Guideline formulation starts once a few insights are available. While experts are in the process of extracting new insights and guidelines are being formulated using available insights, application developers continue to build applications to satisfy requirements using available expertise and interfaces from existing technology. Whenever guidelines become available, application developers shift to evaluating them and at the same time benefit from the orientation offered. Technology development starts when application developers realize that recommended implementation methods in guidelines have lower productivity than alternatives and present ideas for improvement.

Since the workflow to generate guidelines is explicit, the set of guidelines defined during the project is not fixed. It can grow continuously by including new guidelines, by evaluating guidelines in new applications, and by making implementation methods more productive. This enables the outcomes of the project to have a long-term and far-ranging impact. We envision that the workflow will be administered beyond the project by the ecosystem of stakeholders created during the project.

As defined through this process, a guideline captures a part of the knowledge corresponding to a very specific topic through a particular experience. Because of this way to capture guidelines, it might not be generic enough at its first stage to be applicable to any development.

Therefore, a methodology was defined to measure the general usefulness of the guidelines.

| DATE:      | 15/05/2018                                    |

|------------|-----------------------------------------------|

| Reference: | TULIPP project – Grant<br>Agreement n° 688403 |

2

PAGE: 27/115

**Copyright TULIPP CONSORTIUM**

ISSUE:

#### 2.2 Methodology to select guidelines

The process of creating new guidelines is not as easy as it might seem from far. The main difficulty is to issue insightful guidelines that will impact a wide number of developers. While the process for creating guidelines start from particular practice or issues, a more general and global view of the problem as well as a higher level of information is required. We defined the following methodology to derive from the individual experiences gained while developing platforms and applications guidelines with general usefulness meanings.

Four steps have been defined to review and improve the quality of guidelines: (1) each guideline is reviewed and (2) a report is written during this review. If the guideline has enough potential to be added to the guideline database, thanks to the review report, the quality of the guideline is improved (3) and the guideline is added to the guideline database (4).

#### 2.2.1 STEP 1: the Guideline Quality Assurance Board

To assess the quality of the collection of guidelines, the first step is to identify to whom the guidelines is intended - e.g. application developer or hardware designer - while this person is the best qualified one that can assess the insightfulness of the guideline in the utilisation context. Note that there might be more than one person addressed by a guideline and therefore more than one person that will assess the quality of the guideline. We refer to this set of persons as the Guideline Quality Assurance Board.

The work package leader of WP1 is in charge of identifying the type of persons addressed by the guideline and assigns, in collaboration with the partners, the review of the guideline to the best suitable person in the consortium. When the leader of WP1 cannot identify the type of persons addressed by the guideline, the executive board of the project will be assigned the task and will decide to whom the guideline is addressed or if the guideline has to be dropped due to a lack of significance.

Each guideline has a specific quality assurance board composed of experts<sup>1</sup> from at least one of the following groups:

- <u>HW designers</u>: dealing with the design of the hardware platform, the components choices and the interfaces according to system requirements.

- OS designers: dealing with the operating system design and development facing the need to bring standard APIs for applications and making the OS work on the hardware platform while bringing the application the means to efficiently control the hardware behaviour.

<sup>&</sup>lt;sup>1</sup> Note that a single person can have expertise in multiple areas and therefore fill different roles in the guideline evaluation board. However, an expert is always given a designated area to focus on when evaluating a guideline to ensure that all aspects of the guideline are fully addressed.

- <u>Toolchain designers:</u> dealing with the application developers. They must bring a comprehensive tool that allows the application designer to efficiently map the application on the hardware.

- <u>Application developers:</u> knowing the algorithms behind an application and having the ability to develop the code on the chosen hardware. They understand the complete stack and can make use of the tool to develop faster the application.

- <u>System architect:</u> dealing with the whole system definition from the definition of the

constraints that comes from the final product, having in mind the targeted price of the solution

and able to understand integration issues that come with any choice from the other four

groups.

- The current list of experts is provided in Appendix 11 Guidelines evaluation experts.

#### 2.2.2 STEP 2: Quality Assurance report

The assessment will lead to a quality assurance report that will assess the quality of the guidelines.

The report has several goals and will address them all:

- It identifies the type of person to whom the guideline is intended

- It identifies the expertise domains required to write the guideline

- It points out the parts of the guidelines that are e.g. too restrictive or too use-case specific.

- It identifies the parts of the handbook (and also D1.3) that refer to the given guideline

- It identifies the work done in the project that is benefit from the guideline

We rely on the wiki to write the quality assurance report

The outcome of the evaluation is a decision on if the guideline has sufficient quality to become part of the TULIPP guideline database.

#### 2.2.3 STEP 3: The Guideline Improvement Expert Board

If the guideline is not of sufficient quality, the quality assurance board will assign an expert of the topic addressed by the guideline. The expert will be in charge of taking the comments into account and will improve the guideline quality.

There might be more than one domain of expertise and therefore more than one expert required. We refer to this group of expert as the guideline improvement expert board.

When the board is composed of more than one expert, one of them will be assigned as the leader of the guideline evolution and will be responsible for integration of the contributions of others.

When the board is convinced that the guideline has reached sufficient quality, it is provided to the guideline quality assurance board for a new assessment.

#### 2.2.4 STEP 4: The guidelines database and guideline references

When the guideline quality is improved, it is then integrated to the final guidelines database that comes together with the starter kit.

Following the evaluation report, the final handbook but also some of the project deliverables will be updated with references to corresponding guidelines. This applies mainly to D1.3 and the final review report D7.2.

Compose the guideline evaluation board with experts from the consortium

Produce the evaluation report

Rework the guideline to improve its quality following the evaluation report

Reference the guideline in the book and in the workpackages of the project

Figure 4: Guidelines quality improvement process

| DATE: | 15/05/2018 |  |

|-------|------------|--|

| DAIE. | 15/05/2018 |  |

PAGE: 30/115

**Copyright TULIPP CONSORTIUM**

ISSUE:

#### 3 EMBEDDED COMPUTING CHALLENGES

Embedded computing refers to a computing solution implemented inside a larger object which primary function is not to compute. The object is often mobile, often has to process data from sensors with real-time computing constraints, and often has no direct, or limited, access to any server or bigger computing infrastructures.

Such embedded systems bring functions like control and automation to devices in common use today like mobile phones, washing machines, cameras, peacemakers, TV, alarm clock, GPS... It is evaluated that 98% of all microprocessors are manufactured as components of embedded systems. [Barr, Michael (1/08/2009) "Real men program in C". Embedded Systems Design. TechInsights (United Business Media) p.2].

Even though the spectrum of embedded computing solutions is very wide – from a watch to an aircraft computing system – common characteristics and concerns can still be found when comparing typical embedded computers to general-purpose ones. We can notice that embedded solutions are always fighting with small or highly constrained volume, weight constraints and reduced power consumption or heat dissipation. This is referred as SWaP (Size, Weight and Power) constraints.

These constraints have drastic impact on the computer architecture. The whole computing solution being limited, including the processor capabilities, the memories sizes (RAM as well as flash memory). The storage capabilities are also limited; there is often no hard drive. There is almost always links to sensors and actuators. When the device has access to a network, the basic functions of the device can be extended over the network like e.g. the Google GPS application on Android mobile phones using the network servers to compute the road.

### 3.1 An Image-processing Platform

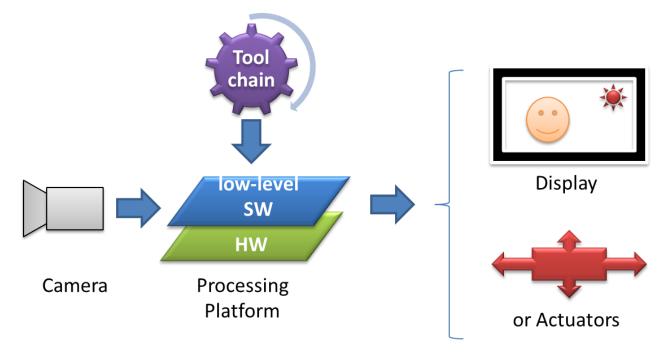

In the general view, an image-processing platform is composed of a hardware device on top of which low-level software is implemented to operate the hardware (e.g. an operating system and application domain libraries) and a set of tools, generally called a tool-chain, must also be available to develop applications.

Such an image-processing platform is dedicated at processing images out of one or several sensors, a sensor being a camera or camera-like device on most of the applications. Through dedicated algorithm, higher-level of information will be extracted from the image. This result might be used in two ways: (1) to produce actions or (2) to output enhanced information with the image.

Since the sensor outputs frames at a given rate, the platform must be able to process images at the same rate not to lose any information. When the result of the computation is not linked to any safety issue, it might be allowed to lose some of the frames but anyway, for the information to have any meaning, the system must be designed to not lose any frame and thus be real-time. Real-time-processing means the system will process the data at the same pace it is produced.

Figure 5: The typical usage for an embedded image processing platform

To achieve this, a holistic view of the system is required so as to achieve the best power efficiency from inevitably highly heterogeneous hardware since the more dedicated the hardware, the better the power efficiency.

This heterogeneity has a cost. While being able to compute more pixels for a given power budget, the programmer loses from genericity and thus programmability and versatility. This means often dedicated programming languages or restricted APIs. Getting the API as close as possible to known and standard APIs eases the learning curve.

When a system gets several computing units, the programmer also has to take into account the scheduling of the tasks on the units and the data transfers between the units. This design step highly benefit from an operating system.

With a power-aware tool chain, the application designer can check, for each mapping of the application tasks on the hardware resources, the impact on power consumption. He or she can thus schedule the

| REFERENCE: | Тицір project – Grant<br>Agreement n° 688403 |

|------------|----------------------------------------------|

| DATE:      | 15/05/2018                                   |

| ISSUE:     | <b>2</b> PAGE: 32/115                        |

processing chain to optimize both the performance and the required energy. The tool chain would rely on the low-power real-time operating system specifically designed to fit in the small memory sizes of embedded devices. The operating system would come with an optimized implementation of necessary set of common image processing libraries and allows a seamless scheduling of the application on the hardware chips.

#### 3.2 Medical Challenges

As defined by the physicians, Medicine is an art based on science. Doctors have to diagnose, to make prognosis and to take decisions based partly on protocols and scientific examination of the patient. The difficulties they face are mostly to be able to understand what's going wrong with only partial information of a human being. The human body is such a complex system that it requires a lot of practice and experience for doctors to deal with it.

Even if medicine is an art, it is a highly technical domain. With always improving technology, the medical staff can benefit from always more accurate measurement and imagery.

Medical imaging is the visualization of body parts, organs, tissues or cells for clinical diagnosis and preoperative imaging. The global medical image processing market is about \$15 billion a year. The imaging techniques used in medical devices include a variety of modern equipment in the field of optical imaging, nuclear imaging, radiology and other image-guided intervention. The radiological method, or x-ray imaging, renders anatomical and physiological images of the human body at a very high spatial and temporal resolution.

Imagery is one of the keys to improve accuracy of diagnosis and reduce the time spent to cure patients. It also allows for faster surgery, smaller cuts in the body and faster patient recovery. All these improvements allow reducing the costs to cure, which is a priority for insurance companies and governments.

X-ray instruments are highly relevant to a significant part of the market share, in particular through the Mobile C-Arm, which is a perfect example of a medical system that improves surgical efficiency. In real time, during an operation, this device displays a view of the inside of a patient's body, allowing the surgeon to make small incisions rather than larger cuts and to target the region with greater accuracy. This leads to faster recovery times and lower risks of hospital-acquired infection. The drawback of this is the radiation dose: 30 times what we receive from our natural surroundings each day. This radiation is received not only by the patient but also by the medical staff, week in, week out.

The fact this device takes pictures continuously, implies x-rays are going through the patient continuously. Since x-rays cannot be narrowed to the zone of interest, the radiation goes not only on

| REFERENCE: | TULIPP project – Grant<br>Agreement n° 688403 |

|------------|-----------------------------------------------|

| DATE:      | 15/05/2018                                    |

| ISSUE:     | 2 PAGE: 33/115                                |

the body part under operation but also to the whole body of the patient and to the medical staff around the patient.

While the x-ray sensor is very sensitive, lowering the emission dose increases the level of noise on the pictures, making it unreadable. This can be corrected with proper processing.

From a regulatory point of view, the radiation that the patient is exposed to must have a specific purpose. Thus, each photon that passes through the patient and is received by the sensor must be delivered to the practitioner; no frame should ever be lost. This brings about the need to manage side by side strong real-time constraints and high-performance computing.

We managed to lower the radiation dose by 75% and restore the original quality of the picture thanks to specific noise reduction algorithms running on high-end PCs. However, this is unfortunately not convenient when size and mobility matter, such as in a confined environment like an operating theatre, crowded with staff and equipment.

Yet by providing the computing power of a standard Intel core-i7 PC in a device the size of a smartphone, TULIPP makes it possible to lower the radiation dose while maintaining picture quality.

#### 3.3 UAV, Drones Challenges

Small unmanned aerial vehicles (UAVs) enter in more and more applications like surveillance and rescue, video production, logistics, research, etc.

The usage of such systems in the entertainment domain is growing especially fast. This development is boosted by the constantly rising commercial market for small UAVs providing broad accessibility, diversity and low costs. Essential enhancements to UAV usage are expected from improvement to their capabilities; perception and intelligent evaluation of the environment make many new applications possible. But more intelligence means more computing power which in turns means more weight and energy consumption. These are however very limited for small UAVs.

As always, each technology comes along with drawbacks and potential for abuse and this is in particular true for UAVs. With the growing number of UAVs, the number of crashes caused by malfunction or maloperation also increases. In the worst case it might cause damages to people, goods and infrastructure. Furthermore, with the broad availability and low cost aspect of UAVs, a common and unforeseeable use (and misuse as well) of this technology is expected in the private sector.

UAVs with automatic collision avoidance will help to reduce those risks.

The UAV use case in TULIPP deals with estimation of depth from two images produced by stereo cameras in order to detect objects and to avoid a collision in further steps. There already exist a lot of algorithms for estimating depth or distance range from different sensors for collision avoidance. In contrast to laser scanners, which are quite robust but expensive, stereo cameras weigh less and are much cheaper. In TULIPP, we focus on user friendly and adjustable depth-map generation which can be used easily for object detection and collision avoidance. While implemented on UAVs, the technology is easily portable for other application on other vehicles and particularly cars.

Obstacle detection is needed to avoid collisions with motionless or moving obstacles on the flight lane and is indispensable for autonomous flight. Most of the small UAVs fly with velocities up to 60 km/h (10 m/s), but some of them can fly with velocities up to 180 km/h (30 m/s) and even more. The stopping distance is strongly dependent from the velocity, the type of the UAV and the payload. With the "usually" velocity of about 30 km/h of a common type of "multicopter", the stopping distance is less than 5 metres, but with more extreme UAVs it can be up to 50 metres. The size of a dangerous obstacle is usually over 5 cm (Figure 6 a), but in some cases obstacles with sizes of as less as 2 mm, more difficult to detect, can also be dangerous (Figure 6 b-c).

Figure 6: Different obstacles in typical environments of UAVs

The use case solution "collision avoidance" must support the following functions:

- 1. Real-time pictures collection by two cameras and additionally pictures synchronization of both pictures.

- 2. Real-time stereo depth map computation and distance measure to object in flight path.

- 3. Getting the current position and flying route from UAV control unit.

- 4. Detection of objects which are on the current air route of the UAV and can cause a collision. The relevance of object is dependent on the distance to the object, velocity of the fly and sizes of the object.

- 5. Calculation of a new safe (free from obstacles) air route taking into account inaccuracies of the computed depth information and possible variations of the UAV from the planned trajectory.

- 6. Transfer of the new route to the UAV control unit.

All these heterogeneous functions must work in real time, and the TULIPP solution ensures it by its good balance of weight, performance and power consumption.

#### 3.4 ADAS Challenges

Advanced driver-assistance systems (ADAS) while helping the driver to focus on what's important on the road are developing at a very fast pace. Sustained by the now ready, available and good-enough technology, devices are embedding more and more intelligence to analyse the driver and its environment and might even act and control the car in case of danger.

Since this technology saves lives, it is strongly supported by governments and insurance companies for it will not only save people but reduce insurance costs, infrastructure damages and medical care to injured people.

Having more electronic devices in a car has also drawbacks leading to big challenges. The first challenge is the power consumption. With more electronics, more power in drained to feed the chips and this becomes even worth when more computation and 'bigger' processors are required.

A second challenge is the number of sensor that is also increasing at a fast peace. More cameras are going to be implemented to understand the whole environment of the car but also to interpret the behaviour of the passengers and to oversee the driver's actions. Images will also be linked with other sensors in the car and sensor fusion algorithms will be required for the car to get a full understanding of the situation and take the right decision.

This second challenge also comes with a price challenge. The technology is yet developed on high-end cars, but comes fast after only few years to the consumer market. If the target price of the first version is not a problem, its implementation on regular cars must be as cheap as possible. This market is the real final goal while this is where the highest return on Invest is expected.

A third challenge is the ability to foresee situations before they are actually encountered. To this goal, the car must be able to predict the behaviours of the other cars. This can be achieved by communicating cars but, since the traffic is also shared with legacy cars, it must also rely on advanced techniques to analyse the behaviour from what the car sees, just like humans do. Humans do learn

| REFERENCE: | TULIPP project – Grant<br>Agreement n° 688403 |

|------------|-----------------------------------------------|

| DATE:      | 15/05/2018                                    |

ISSUE: 2 PAGE: 36/115

#### **Copyright TULIPP CONSORTIUM**

during many years after their driving licence exam to be able to anticipate the behaviours of others. The cars will also have to develop learning capabilities.

All this pushes the technology to develop more image processing chips and algorithms, but also the ability to interpret the image, not only with former processing algorithms, but also with higher level of perception like what is today developed through neural networks.

The demand for more computing power at a reduced power budget, or better said a higher processing efficiency, and cost-effective solutions are crucial for this market to develop.